PCI-SIG demuestra la interoperabilidad PCIe 6.0 en FMS 2024

16/08/2024

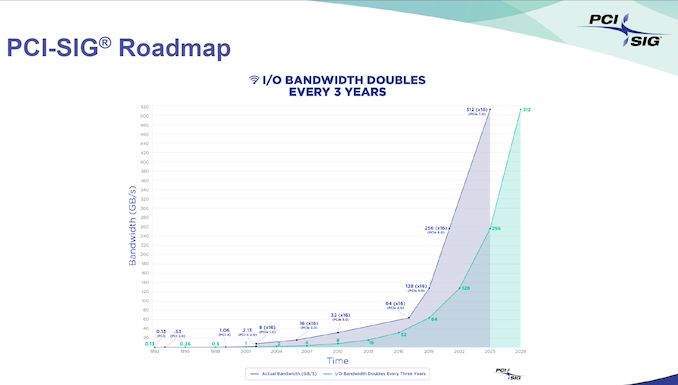

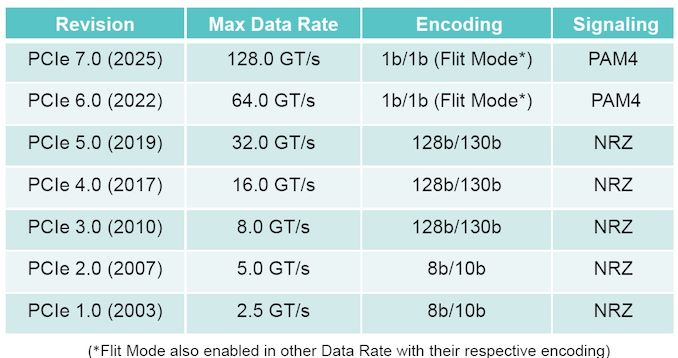

A medida que la implementación de PCIe 5.0 gana impulso en los centros de datos y los mercados de consumo, PCI-SIG no se queda quieto y ya está trabajando para preparar el ecosistema para las actualizaciones de las especificaciones PCIe. En FMS 2024, algunos proveedores incluso hablaron de PCIe 7.0 con sus capacidades de 128 GT/s, mientras que PCIe 6.0 ni siquiera ha comenzado a distribuirse todavía. Nos reunimos con PCI-SIG para conocer sus actividades y discutir el estado actual del ecosistema PCIe.

PCI-SIG ya ha puesto a disposición de sus miembros las especificaciones PCIe 7.0 (v 0.5) y espera que las especificaciones completas se publiquen oficialmente en 2025. El objetivo es proporcionar un rendimiento de datos de 128 GT/s con hasta 512 Gbps de velocidad bidireccional. tráfico mediante enlaces x16. Al igual que PCIe 6.0, esta especificación también utilizará la señalización PAM4 y mantendrá la compatibilidad con versiones anteriores. La eficiencia energética y el área del chip de silicio también se consideran parte del proceso de redacción.

El cambio a la señalización PAM4 da como resultado tasas de error de bits más altas en comparación con el esquema NRZ anterior. Esto hizo necesario adoptar un esquema de corrección de errores diferente en PCIe 6.0: en lugar de operar en paquetes de longitud variable, la codificación de la unidad de control de flujo (FLIT) de PCIe 6.0 opera en paquetes de tamaño fijo para facilitar la corrección de errores hacia adelante. PCIe 7.0 conserva estos aspectos.

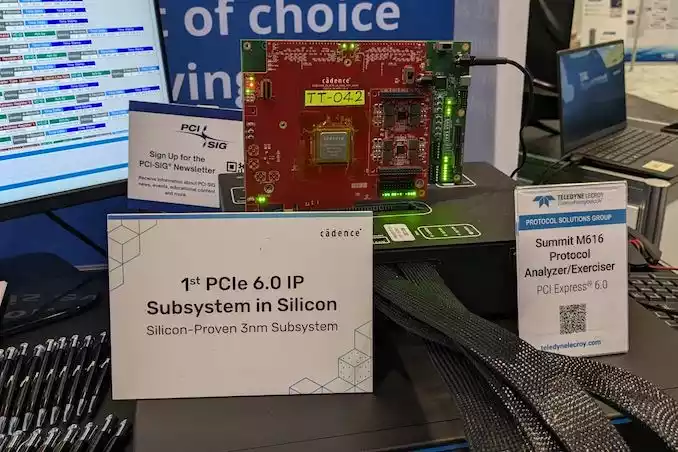

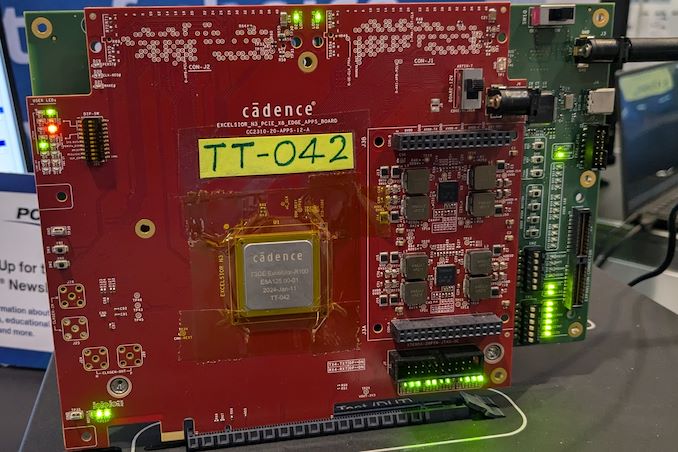

También se espera que la lista de integradores para el programa de cumplimiento PCIe 6.0 se publique en 2025, aunque las pruebas iniciales ya están en marcha. Esto quedó demostrado en la demostración de FMS 2024 que involucró el chip de prueba de 3 nm de Cadence para su oferta IP PCIe 6.0, así como el analizador PCIe 6.0 de Teledyne Lecroy. Estos cronogramas se alinean bien con las fechas de finalización de las especificaciones y la disponibilidad del programa de cumplimiento para generaciones anteriores de PCIe.

También recibimos una actualización sobre el Grupo de Trabajo de Óptica. Aunque es independiente de la tecnología óptica, el grupo de trabajo también tiene la intención de desarrollar factores de forma específicos de la tecnología, incluidos transceptores ópticos conectables, ópticas integradas, ópticas empaquetadas y E/S ópticas. Las capas lógicas y eléctricas de las especificaciones PCIe 6.0 se están mejorando para adaptarse a la nueva estandarización óptica PCIe y este proceso también se realizará con PCIe 7.0 para coincidir con el lanzamiento de este estándar el próximo año.

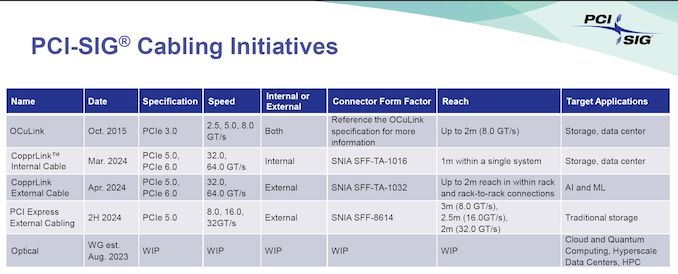

PCI-SIG también lidera iniciativas de cableado. Del lado del consumidor, hemos visto una tracción significativa para Thunderbolt y las carcasas de GPU externas. Sin embargo, incluso los centros de datos y los sistemas empresariales están avanzando hacia soluciones de cableado a medida que queda claro que desagregar componentes como el almacenamiento de CPU y GPU es mejor para el diseño térmico. Además, mantener la integridad de la señal a largas distancias resulta difícil para los rastros de señales a bordo. El cableado interno de los sistemas informáticos puede ayudar aquí.

OCuLink demostró ser un buen candidato y fue adoptado ampliamente como enlace interno en sistemas de servidores. Incluso apareció en miniPC de algunos fabricantes chinos en su forma externa destinada al mercado de consumo, aunque su éxito fue limitado. A medida que aumentan las velocidades, será imperativo adoptar un estándar ampliamente para dispositivos PCIe externos (o incluso para conectar componentes dentro de un sistema).

Si quieres conocer otros artículos parecidos a PCI-SIG demuestra la interoperabilidad PCIe 6.0 en FMS 2024 puedes visitar la categoría Noticias MiniPC.

Deja una respuesta